Vol.14, No.2, 2024

## DEVELOPMENT OF I<sup>2</sup>C LEVEL SHIFTER USING µASIC

### Danylo Talanchuk<sup>1</sup>, Vitalii Rybotytskyi<sup>2</sup>, Stepan Nichkalo<sup>1</sup>, Anatoly Druzhinin<sup>1</sup>

<sup>1</sup> Lviv Polytechnic National University; <sup>2</sup> Atlas Magnetics Ukraine danylo-hryhorii.talanchuk.mnmnm.2024@lpnu.ua, ribotetskiy@gmail.com, stepan.i.nichkalo@lpnu.ua, anatolii.o.druzhynin@lpnu.ua

https://doi.org/10.23939/jcpee2024.02.006

Abstract: This paper presents the design and implementation of an I<sup>2</sup>C level shifter using the AM1U1420 single-chip solution. The device enables seamless voltage translation between different I<sup>2</sup>C logic levels, ensuring reliable communication between components operating at varying supply voltages. The AM1U1420 can integrate bidirectional level shifting functionality, reducing the need for external components and simplifying circuit design. We analyze its electrical characteristics, performance metrics, and practical application scenarios. Experimental results confirm the chip's efficiency in maintaining signal integrity and low propagation delay. This solution is particularly beneficial for modern embedded systems, IoT devices, and mixed-voltage environments.

**Key words:** I<sup>2</sup>C, level shifter, power consumption, clock, CMOS, μASIC, IoT device.

#### 1. Introduction

The I<sup>2</sup>C (Inter-Integrated Circuit) bus is widely used for communication between low-speed peripheral devices in embedded systems, sensors, and microcontrollers. However, as modern electronics increasingly incorporate components operating at different voltage levels, reliable voltage translation is essential to ensure proper communication. Traditional level-shifting solutions often require multiple discrete components, increasing circuit complexity and board space.

The AM1U1420 can be used as single-chip level shifter and provide an efficient and compact solution for bidirectional voltage translation in I<sup>2</sup>C applications. It enables seamless communication between devices operating at different voltage domains, reducing design complexity and improving system reliability. This paper explores the functionality, implementation, and performance of the AM1U1420, demonstrating its advantages over conventional level-shifting methods. Experimental results validate their effectiveness in maintaining signal integrity and low propagation delay, making it an ideal choice for embedded systems, IoT applications, and mixed-voltage environments.

Level shifting for I<sup>2</sup>C communication has been extensively studied, with various approaches proposed to ensure compatibility between devices operating at different voltage levels. Traditional solutions often rely on

external pull-up resistors and MOSFET-based circuits to achieve bidirectional voltage translation. For example, the classic BSS138-based level shifter is widely used due to its simplicity and low cost. However, such discrete implementations can introduce signal degradation, increased propagation delay, and the need for careful resistor selection to balance speed and power consumption [1].

Several dedicated level-shifting ICs, such as the PCA9306 [2] and TXB0108 [3], have been developed to address these challenges, offering integrated solutions for I<sup>2</sup>C and other low-speed digital interfaces. These ICs improve performance by incorporating built-in pull-ups, low on-resistance, and adaptive drive strength. However, many existing solutions still require external components, occupy significant board space, or lack optimized power efficiency for modern applications.

The AM1U1420 represents a more advanced alternative by integrating bidirectional I<sup>2</sup>C level shifting into a single compact package. Unlike traditional solutions, it minimizes external component requirements while maintaining high signal integrity and low power consumption. This paper builds upon previous work by evaluating the AM1U1420's performance in real-world applications, comparing it with existing methods, and highlighting its advantages in embedded system design.

The I²C bus is a widely used for short-distance communication between integrated circuits. Developed by Philips (now NXP Semiconductors), I²C enables multiple devices, such as microcontrollers, sensors, memory chips, and displays, to communicate using only two signal lines: SDA (Serial Data Line) and SCL (Serial Clock Line). This simplicity makes it ideal for embedded systems, IoT devices, and consumer electronics.

I<sup>2</sup>C operates on a master-slave architecture, where one or more master devices control communication with multiple slaves. The bus supports multiple data rates, including Standard Mode (100 kbps), Fast Mode (400 kbps), Fast Mode Plus (1 Mbps), and High-Speed Mode (3.4 Mbps) [5]. Each device on the bus is assigned a unique address, allowing efficient data exchange using a defined protocol.

A key feature of I<sup>2</sup>C is its open-drain design, where pull-up resistors are required to maintain proper voltage levels. This design enables multiple devices to share the same bus while avoiding signal contention. However, when devices operate at different voltage levels (e.g., 1.8 V and 3.3 V), voltage level shifting is necessary to ensure reliable communication.

To address this challenge, various level-shifting techniques have been developed, ranging from simple MOSFET-based circuits to dedicated level-shifter ICs. The AM1U1420, discussed in this paper, offers an integrated, efficient solution for bidirectional I<sup>2</sup>C voltage translation, simplifying design and enhancing system reliability.

The  $\mu$ ASIC family consists of programmable ultrasmall mixed-signal ICs that include logic macrocells, I<sup>2</sup>C interface, oscillators, ACMPs, a temperature sensor, a voltage reference (VREF), and other features.

In this study, we used the AM1U1420, an ultra-small programmable  $\mu ASIC$ . Each macrocell within the AM1U1420 offers multiple configurable settings and initial states, providing maximum flexibility for various applications. Main features [6]:

- 1.71 V to 5.5 V supply ( $V_{DD}$ ).

- $1.10 \text{ V to V}_{DD}(V_{DD2}).$

- Operating temperature range: -40 °C to 85 °C.

- RoHS compliant/Halogen-free/Pb-free.

- Contains 4 analog comparators (ACMP).

- Has voltage reference  $(V_{REF})$ .

- Temperature sensor (TS).

- I<sup>2</sup>C Protocol compliant

- Twenty-seven multifunctional macrocells.

- Two oscillators.

- Power on reset.

- Data protection features:

- CRC-8;

- Continuous register verification.

#### 2. Experimental part

# 2.1. Implementation of I<sup>2</sup>C level shifter on AM1U1420

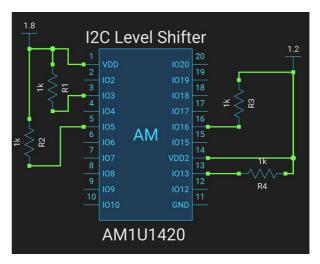

The  $I^2C$  level shifter on the  $\mu ASIC$  utilizes a single IC-AM1U1420-along with four resistors that pull up the PMOS output to the voltage source. Adjusting the resistance of these resistors impacts power consumption and the strength of the pull-up.

The I<sup>2</sup>C interface relies solely on an open-drain NMOS output. Since both SDA and SCL are bidirectional, both the master and slave can pull the signals LOW.

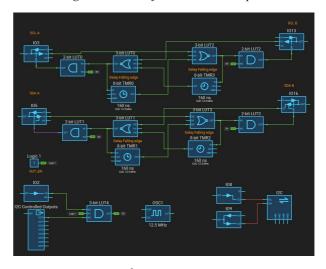

The µASIC was configured by using Atlas EDA.

The examples of I<sup>2</sup>C level shifter schematics and its design configuration are presented in Fig. 1 and Fig. 2. This configuration is designed exclusively for I<sup>2</sup>C, utilizing an open-drain NMOS output. The oscillator (OSC1) is set to auto mode, meaning it activates only when a signal is present. Each level shifter channel

automatically detects the direction of communication by sensing which line is pulled LOW first. Upon power-up, all I/O pins default to input mode, waiting for a signal. After the signal transition, the I/O pins remain in input mode, awaiting further signals. Additionally, there is an option to disable outputs via IO2 or through an I<sup>2</sup>C command.

Fig. 1.  $I^2C$  level shifter schematic example.

Fig. 2. I<sup>2</sup>C level shifter design.

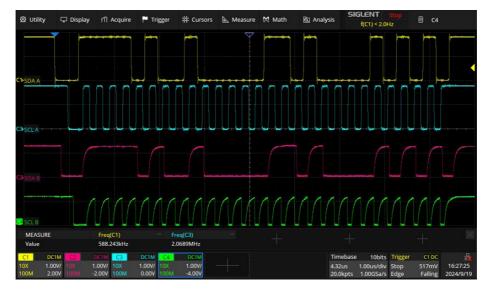

The experimets were carried out with next the following conditions:

- Temperature: room temperature (25 °C).

- $-V_{DD} = 1.8 \text{ V}.$

- $-V_{DD2} = 1.2 \text{ V}.$

- Scope probe capacitance: 11 pF.

- Scope input capacitance: 17 pF.

- Channel 1 (yellow) I<sup>2</sup>C SDA A 1.8V (IO5).

- Channel 2 (blue) I<sup>2</sup>C SCL A 1.8V (IO3).

- Channel 3 (magenta) I<sup>2</sup>C SDA B 1.2V (IO16).

- Channel 4 (green) I<sup>2</sup>C SDA A 1.2V (IO13).

In Figs. 3–5 we see the output test of the device.

Fig. 3. I<sup>2</sup>C Level shifter scope shot, 3.4 MHz frequency (A to B transition).

Fig. 4. I<sup>2</sup>C Level shifter scope shot, 3.4 MHz frequency (B to A transition).

Fig. 5. I<sup>2</sup>C Level shifter scope shot, 3.4 MHz frequency (outputs disable).

Table 1

#### 3. Analysis of current consumption

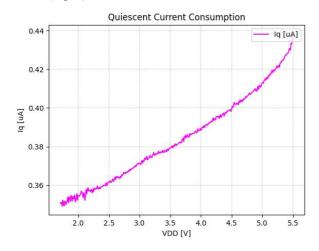

In Quiescence, the chip consumes a small amount of current (Fig. 6).

Fig. 6. Quiescent current consumption.

The results of Fig. 6 are summarized in Table 1.

## Quiescence current consumption

| $V_{DD}, V$ | $I_g, \mu { m A}$ |

|-------------|-------------------|

| 1.71        | 0.350             |

| 1.8         | 0.351             |

| 3.3         | 0.376             |

| 5.0         | 0.413             |

| 5.5         | 0.438             |

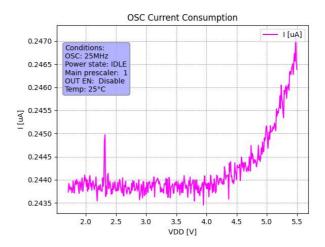

The  $\mu$ ASIC consumes an ultra-low amount of power, with its internal oscillators being the primary contributors to power consumption. To minimize this, it is crucial to stop OSC1 when no signal is present. Auto mode handles this by putting the oscillator into an IDLE state when there is no signal on the timers or any signal forcing activation. In this state, power consumption is significantly reduced to just 250 nA at  $V_{DD} = 3.3$  V.

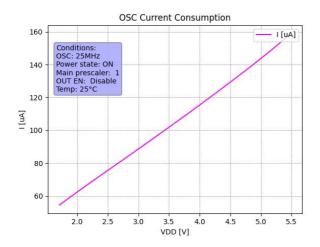

Fig. 7. OSC1 current consumption ON state.

Fig. 8. OSC1 current consumption IDLE state.

The results of the oscillator current consumption are summarized in Table 2. As it follows, when sending packages, current consumption rises. It also depends on operating voltages. The higher  $V_{DD}$  – the higher current consumption (Figs. 7, 8).

Table 2

Current consumption of oscillator

| OSC    |        |       |       |        |        | Unit |

|--------|--------|-------|-------|--------|--------|------|

| Mode 1 | 1.71 V | 1.8 V | 3.3 V | 5.0 V  | 5.5 V  | om.  |

| IDLE   | 0.24   | 0.24  | 0.24  | 0.25   | 0.25   | μA   |

| ON     | 44.97  | 46.93 | 77.26 | 113.37 | 125.39 | μΑ   |

#### 4. Conclusion

The experiment demonstrated that a Bidirectional  $I^2C$  level shifter can be successfully implemented using the AM1U1420 chip. This chip has a low quiescent current consumption of 0.35  $\mu A,$  which increases up to 125.39  $\mu A$  during data transmission. A minor measurement error occurred due to the capacitance of the oscilloscope. All experiments were conducted at room temperature. The output signal exhibited a delay of one clock cycle.

To handle Standard mode, Fast mode, Fast mode plus, High-speed mode (1.7 Mbit/s) 2 MHz oscillator can be used. This will reduce the current consumption significantly.

#### References

- [1] Frederick M. Cady Microcontrollers and Microcomputers Principles of Software and Hardware Engineering, Oxford University Press, Incorporated, 2009.

- [2] Texas Instruments, "PCA9306: Dual-Bidirectional I<sup>2</sup>C Level Translator", Datasheet, 2021.

- [3] Texas Instruments, "TXB0108: 8-Bit Bidirectional Voltage-Level Shifter", Datasheet, 2019.

- [4] MIPI Alliance, "I<sup>3</sup>C Specification v1.1", *Technical Report*, 2021.

- [5] J. Lee et al., "High-Speed and Low-Power Level Shifter Design for Embedded Systems", *Journal of Semiconductor Technology and Science*, vol. 18, No. 3, pp. 450–462, 2018.

- [6] Atlas Magnetics, "AM1U1420: Ultra-Small Programmable uASIC", Datasheet, n. d.

# РОЗРОБЛЕННЯ І<sup>2</sup>С ПРИСТРОЮ ЗСУВУ РІВНЯ З ВИКОРИСТАННЯМ µASIC

Данило Таланчук, Віталій Риботицький, Степан Нічкало, Анатолій Дружинін

У статті наведено дизайн і реалізацію пристрою зсуву рівня I<sup>2</sup>C із використанням однокристального рішення AM1U1420. Пристрій забезпечує плавний перехід напруги між різними рівнями логіки І<sup>2</sup>С, а також надійний зв'язок між компонентами, що працюють за змінних напруг може інтегрувати живлення. AM1U1420 двонаправленого зсуву рівня, зменшуючи потребу в зовнішніх компонентах і спрощуючи дизайн схеми. Проаналізовано електричні характеристики, показники продуктивності та потенційне практичне застосування пристрою. Експериментальні результати підтверджують ефективність мікросхеми у збереженні цілісності сигналу та низької затримки поширення. Це рішення особливо корисне для сучасних вбудованих систем, пристроїв інтернету речей і пристроїв, що оперують за комбінованих напруг.

**Danylo Talanchuk** – a master student of the Department of Semiconductor Electronics at the Institute of Information and Communication Technologies and Electronic Engineering, Lviv Polytechnic National University, Ukraine. Research interests: design and simulation of output characteristics of sensors, micro- and nanosystem devices.

Stepan Nichkalo – PhD, Associate Professor of the Department of Semiconductor Electronics at the Institute of Information and Communication Technologies and Electronic Engineering, Lviv Polytechnic National University, Ukraine. His scientific activity includes technological features for production of silicon nanowire arrays and their use in micro- and nanoelectronic devices.

Anatoly Druzhinin – D. Sc., professor, Head of the Department of Semiconductor Electronics at the Institute of Information and Communication Technologies and Electronic Engineering, Lviv Polytechnic National University, Ukraine. He is also the winner of Ukrainian State Prize in Science and Technology (2011), Honored Worker of Science and Technology of Ukraine. The main scientific acti-

vities of prof. A. Druzhinin include: theoretical and experimental study of strain-induced effects in silicon, germanium and their solid solutions whiskers. Prof. Druzhinin has authored more than 140 scientific publications indexed in Scopus and Web of Science and more than 50 inventor's certificates and patents. Under his supervision 6 doctors and 11 candidates in technical science were graduated.

**Vitalii Rybotytskyi** – Middle Application Engineer at Atlas Magnetics Ukraine, specializing in uASIC. Holds a Master's degree from Lviv Polytechnic National University, Institute of Information and Communication Technologies and Electronic Engineering.

Received: 02.10.2024, Accepted: 25.12.2024

ORCID ID: 0000-0001-8455-0146 (S. Nichkalo) ORCID ID: 0000-0002-4854-3464 (A. Druzhinin)